|

CMSIS-DAP

Version 2.1.1

Interface Firmware for CoreSight Debug Access Port

|

|

CMSIS-DAP

Version 2.1.1

Interface Firmware for CoreSight Debug Access Port

|

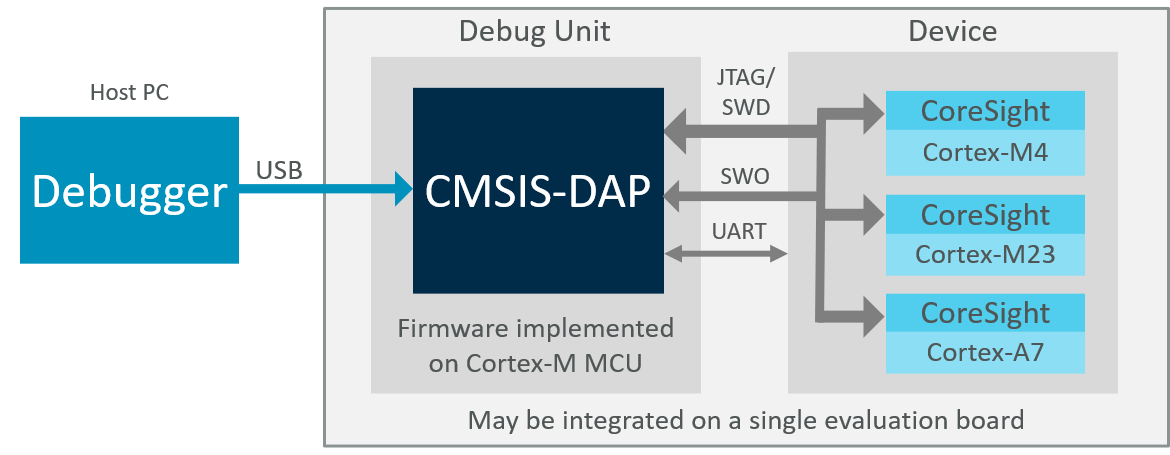

CMSIS-DAP is a protocol specification and a implementation of a firmware that supports access to the CoreSight Debug Access Port (DAP).The various Arm Cortex processors provide CoreSight Debug and Trace. CMSIS-DAP supports target devices that contain one or more Cortex processors. A device provides a Debug Access Port (DAP) typically either with a 5-pin JTAG or with a 2-pin Serial Wired Debug (SWD) interface that connects to a debug unit. CMSIS-DAP is the interface firmware for a debug unit that connects the debug port to USB. Debuggers that execute on a host computer connect via USB and the Debug Unit to the device which runs the application software.

The CMSIS-DAP firmware is provided as source code and is fully configurable to a new debug unit. A source code template and several reference implementations for popular debug units are provided. Refer to Firmware configuration for more information.

The CMSIS-DAP firmware stack is composed of the following components:

In the examples provided, the MDK-Middleware USB stack has been used. However, it is possible to use alternative USB stacks.

CMSIS-DAP compliant debug units must be validated using the scripts provided in Validate the debug unit operation.

The CMSIS-DAP firmware is provided in the following directory structure.

| Directory | Description |

|---|---|

| .\CMSIS\DAP\Firmware\Config | CMSIS-DAP firmware configuration |

| .\CMSIS\DAP\Firmware\Examples | CMSIS-DAP firmware adapted to various debug units |

| .\CMSIS\DAP\Firmware\Include | CMSIS-DAP firmware header file |

| .\CMSIS\DAP\Firmware\Source | CMSIS-DAP firmware source code |

| .\CMSIS\DAP\Firmware\Template | Interface templates for MDK-Middleware |

| .\CMSIS\DAP\Firmware\Validation | Validation project |