The following section contains technical information about RTX v5.

Keil RTX5 is developed and tested using the common toolchains and development environments.

Current development is verified to work with the following toolchains versions:

But in most cases, RTX would work well with other versions of these toolchains as well.

RTX assumes a fully functional processor and uses the following hardware features. It does not implement any confidence test for processor validation which should be provided by an user-supplied software test library.

| Hardware Requirement | Description |

|---|---|

| SysTick timer | The SysTick timer generates the kernel tick interrupts and the interface is implemented in os_systick.c using the OS Tick API |

| Exception Handler | RTX implements exception handlers for SVC, PendSV, and SysTick interrupt |

| Core Registers | The processor status is read using the following core registers: CONTROL, IPSR, PRIMASK |

| System Control Block (SBC) | To control and setup the processor exceptions including PendSV and SVC |

| Interrupt Control | The CMSIS-Core functions __disable_irq and __enable_irq to control the interrupt system via the CPSR core register. |

The RTX implements interfaces to the processor hardware in following files:

Note

- The CMSIS-Core variable SystemCoreClock is used by RTX to configure the SysTick timer.

RTX assumes a fully functional processor and uses the following hardware features:

| Hardware Item | Requirement Description |

|---|---|

| SysTick timer | The SysTick timer shall be available in the processor. |

| System Exceptions | The RTX requires SVC, PendSV, and SysTick exceptions and implements corresponding exception handlers. |

| Core Registers | The RTX uses CONTROL, IPSR , PRIMASK and BASEPRI core registers for reading processor status. |

| System Control Block (SCB) | The RTX uses SCB registers to control and setup the processor system exceptions including PendSV and SVC. |

| NVIC Interface | CMSIS-Core function NVIC_GetPriorityGrouping is used by the RTX to setup interrupt priorities. |

| LDREX, STREX instructions | Exclusive access instructions LDREX and STREX are used to implement atomic execution without disabling interrupts. |

The interface files to the processor hardware are:

Note

- The CMSIS-Core variable SystemCoreClock is used by RTX to configure the SysTick timer.

| Hardware Requirement | Description |

|---|---|

| Timer Peripheral | An arbitrary timer peripheral generates the kernel tick interrupts. The interfaces for Cortex-A Generic Timer and Private Timer are implemented in os_tick_gtim.c and os_tick_ptim.c using the OS Tick API |

| Exception Handler | RTX implements exception handlers for SVC, IRQ, Data Abort, Prefetch Abort and Undefined Instruction interrupt. |

| Core Registers | The processor status is read using the following core registers: CPSR, CPACR and FPSCR. |

| LDREX, STREX instruction | Atomic execution avoids the requirement to disable interrupts and is implemented via exclusive access instructions. |

| Interrupt Controller | An interrupt controller interface is required to setup and control Timer Peripheral interrupt. The interface for Arm GIC (Generic Interrupt Controller) is implemented in irq_ctrl_gic.c using the IRQ Controller API. |

The interface files to the processor hardware are:

Note

- The CMSIS-Core variable

SystemCoreClockis used by RTX to configure the timer peripheral.

RTX requires RAM memory that is accessible with contiguous linear addressing. When memory is split across multiple memory banks, some systems do not accept multiple load or store operations on this memory blocks.

RTX does not implement any confidence test for memory validation. This should be implemented by an user-supplied software test library.

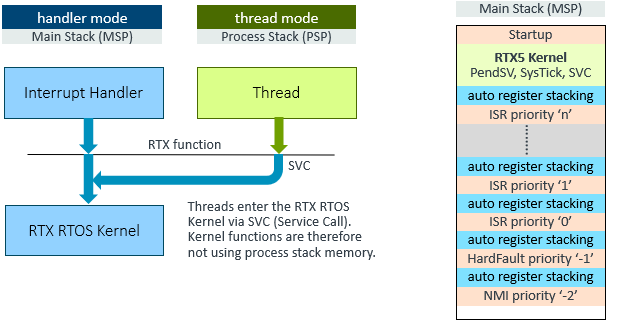

Keil RTX v5 kernel functions are executed in handler mode (using PendSV/SysTick/SVC) and the table below lists the maximum stack requirements for the Main Stack (MSP) that the user should consider.

The stack for the osKernelStart function is referred as "Startup" and RTX v5 uses 32 bytes (with Arm Compiler). However the user should also consider additional stack that might be allocated by the main function of the embedded application. The following picture shows a worst-case memory allocation of the Main Stack.

The stack requirements depend on the compiler and the optimization level. RTX v5 supports event annotations and this configuration impacts also the stack requirement.

Application note KAN316: Determining the stack usage of applications describes the stack usage in RTX applications , explains how to analyze actual stack consumption and find the optimal setting.

Arm Compiler ARMCC V6.20: Main Stack requirements for PendSV/SysTick/SVC

| Optimization | RTX Kernel | RTX Kernel + Event Recorder |

|---|---|---|

| -O1 (Debug) | 96 bytes | 224 bytes |

| -Os (Balanced) | 100 bytes | 232 bytes |

| -Oz (Size) | 104 bytes | 248 bytes |

Keil RTX v5 specific control block definitions (including sizes) as well as memory pool and message queue memory requirements are defined in the header file rtx_os.h:

If you provide memory for the RTOS objects, you need to know the size that is required for each object control block.

The memory of the control block is provided by the parameter attr of the relatedosXxxxNew function. The element cb_mem is the memory address, cb_size is the size of the control block memory.

Refer to Static Object Memory for more information.

The following table lists the control block sizes:

| Category | Control Block Size Attribute | Size | #define symbol |

|---|---|---|---|

| Thread Management | cb_mem | 80 bytes | osRtxThreadCbSize |

| Timer Management | cb_mem | 32 bytes | osRtxTimerCbSize |

| Event Flags | cb_mem | 16 bytes | osRtxEventFlagsCbSize |

| Mutex Management | cb_mem | 28 bytes | osRtxMutexCbSize |

| Semaphores | cb_mem | 16 bytes | osRtxSemaphoreCbSize |

| Memory Pool | cb_mem | 36 bytes | osRtxMemoryPoolCbSize |

| Message Queue | cb_mem | 52 bytes | osRtxMessageQueueCbSize |