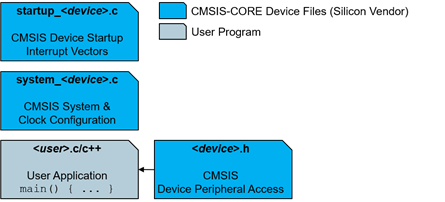

To use the CMSIS-Core (Cortex-M) in an embedded software project at the following CMSIS-Core Device Files need to be added to the application:

The Startup File startup_<Device>.c is executed after reset and calls SystemInit() in the reset hander. After the system initialization the control is transferred to the C/C++ run-time library which performs initialization and calls the main function in the user code. In addition the Startup File startup_<Device>.c contains all exception and interrupt vectors and implements a default function for every interrupt. It may also contain stack and heap configurations for the user application.

The System Configuration Files system_<Device>.c and system_<Device>.h performs the setup for the processor clock. The variable SystemCoreClock indicates the CPU clock speed. In addition the file may contain functions for the memory BUS setup and clock re-configuration.

Note

- The files Startup File startup_<Device>.c and System Configuration Files system_<Device>.c and system_<Device>.h may require application specific adaptations and therefore should be copied into the application project folder prior configuration.

The Device Header File <Device.h> provides access to the following device-specific functionalities:

The easiest way to use CMSIS-Core in a project is with CMSIS Packs.

The CMSIS-Core Device Files are typically provided in a CMSIS Device Family Pack (DFP) that is maintained by the chip vendor for the target device family. The list of public CMSIS packs (including DFPs) can be found at keil.arm.com/packs.

A Device Family Pack (DFP) usually has a requirement for using the CMSIS:CORE component from the CMSIS Software pack that contains the CMSIS-Core Standard Files. In such case the CMSIS Software pack needs to be installed as well.

The files Startup File startup_<Device>.c and System Configuration Files system_<Device>.c and system_<Device>.h are typically provided in the DFP as part of Device class in the Startup group and are defined as configuration files, meaning they are copied from the pack into a project folder and can be modifed there if necessary.

The use of Device Header File <Device.h> can be abstracted with the #define CMSIS_header_file provided in RTE_Components.h. This allows to have uniform include code in the application independent of the target device.

Thereafter, the functions described under API Reference can be used in the application.

For example, the following files are provided by the STM32F10x device family pack:

| File | Description |

|---|---|

| ".\Device\Source\ARM\startup_stm32f10x_cl.s" | Startup File startup_<Device>.c for the STM32F10x device variants |

| ".\Device\Source\system_stmf10x.c" | System Configuration Files system_<Device>.c and system_<Device>.h for the STM32F10x device families |

| ".\Device\Include\stm32f10x.h" | Device Header File <Device.h> for the STM32F10x device families |

Delivery in CMSIS-Packs provides more information on how CMSIS-Core files can be delivered in CMSIS Packs.

Examples

Also see Using TrustZone for Armv8-M that details CMSIS-Core support for Arm TrusZone operation on Cortex-M.

A typical example for using the CMSIS layer is provided below. The example is based on a STM32F10x Device.

Most Cortex-M processors provide VTOR register for remapping interrupt vectors. The following example shows a typical use case where the interrupt vectors are copied to RAM and the SysTick_Handler is replaced.

Test and example projects of many software components have a need for implementations that are independent from specific device vendors but still have adaptations for various Arm Cortex-M cores to benefit from their architectural differenceis.

The Cortex_DFP pack provides generic device definitions for standard Arm Cortex-M cores and contains corresponding CMSIS-Core Device Files. These generic Arm devices can be used as a target for embedded programs, with execution, for example, on processor simulation models.

Validation suits and example projects for such components as CMSIS-DSP, CMSIS-RTOS and CMSIS-Core itself use that approach already.

The CMSIS Processor and Core Peripheral files allow also to create generic libraries. The CMSIS-DSP libraries are an example for such a generic library.

To build a generic Library set the define __CMSIS_GENERIC and include the relevant core_<cpu>.h CMSIS CPU & Core Access header file for the processor.

The define __CMSIS_GENERIC disables device-dependent features such as the SysTick timer and the Interrupt System.

Refer to Configuration of the Processor and Core Peripherals for a list of the available core_<cpu>.h header files.

Example:

The following code section shows the usage of the core_<cpu>.h header files to build a generic library for Cortex-M0, Cortex-M3, Cortex-M4, or Cortex-M7 devices.

To select the processor, the source code uses the defines CORTEX_M7, CORTEX_M4, CORTEX_M3, CORTEX_M0, or CORTEX_M0PLUS. One of these defines needs to be provided on the compiler command line. By using this header file, the source code can access the correct implementations for Core Register Access, Intrinsic Functions for CPU Instructions, Intrinsic Functions for SIMD Instructions, and Debug Access.