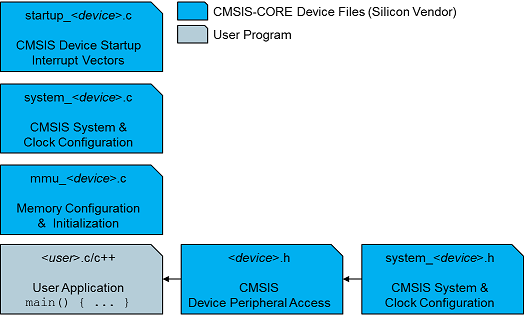

To use the CMSIS-Core-A the following files are added to the embedded application:

Note

- The files Startup File startup_<Device>.c, System Configuration Files system_<Device>.c and system_<Device>.h, Memory Configuration Files mem_<device>.h, and Memory Management Unit Files mmu_<device>.c may require application specific adaptations and therefore should be copied into the application project folder prior configuration. The Device Header File <Device.h> is included in all source files that need device access and can be stored on a central include folder that is generic for all projects.

The Reset_Handler defined in Startup File startup_<Device>.c is executed after reset. The default initialization sequence is

After the system initialization control is transferred to the C/C++ run-time library which performs initialization and calls the main function in the user code. In addition the Startup File startup_<Device>.c contains a weak default handler implementation for every exception. It may also contain stack and heap configurations for the user application.

The System Configuration Files system_<Device>.c and system_<Device>.h performs the setup for the processor clock and the initialization of memory caches, memory management unit, generic interrupt interface and floating point unit. The variable SystemCoreClock indicates the CPU clock speed. System and Clock Configuration describes the minimum feature set. In addition the file may contain functions for the memory bus setup and clock re-configuration.

The Device Header File <Device.h> is the central include file that the application programmer is using in the C/C++ source code. It provides the following features:

The use of Device Header File <Device.h> can be abstracted with the #define CMSIS_header_file provided in RTE_Components.h. This allows to have uniform include code in the application independent of the target device.

The CMSIS-Core-A user files are device specific. In addition, the Startup File startup_<Device>.c is also compiler vendor specific. The various compiler vendor tool chains may provide folders that contain the CMSIS files for each supported device.

Note

- The silicon vendors create these device-specific CMSIS-Core-A files based on CMSIS-Core Device Templates provide by Arm.

Thereafter, the functions described under API Reference can be used in the application.

Examples:

A typical example for using the CMSIS layer is provided below. The example is based on an unspecific Cortex-A9 Device.

The Cortex_DFP pack provides generic device definitions for standard Arm Cortex-A cores and contains corresponding. These generic Arm devices can be used as a target for embedded programs, with execution, for example, on processor simulation models.