Virtual Streaming Interface API for application firmware. More...

Data Structures | |

| struct | ARM_VSI_Type |

| Structure type to access the virtual streaming interface. More... | |

| struct | ARM_VSI_Type.IRQ |

| Interrupt Request (IRQ) More... | |

| struct | ARM_VSI_Type.Timer |

| Time counter with 1MHz input frequency. More... | |

| struct | ARM_VSI_Type.DMA |

| Direct Memory Access (DMA) Controller. More... | |

Macros | |

| #define | ARM_VSI0_BASE (0x4FF00000UL) |

| #define | ARM_VSI1_BASE (0x4FF10000UL) |

| #define | ARM_VSI2_BASE (0x4FF20000UL) |

| #define | ARM_VSI3_BASE (0x4FF30000UL) |

| #define | ARM_VSI4_BASE (0x4FF40000UL) |

| #define | ARM_VSI5_BASE (0x4FF50000UL) |

| #define | ARM_VSI6_BASE (0x4FF60000UL) |

| #define | ARM_VSI7_BASE (0x4FF70000UL) |

| #define | ARM_VSI0 ((ARM_VSI_Type *)ARM_VSI0_BASE) |

| #define | ARM_VSI1 ((ARM_VSI_Type *)ARM_VSI1_BASE) |

| #define | ARM_VSI2 ((ARM_VSI_Type *)ARM_VSI2_BASE) |

| #define | ARM_VSI3 ((ARM_VSI_Type *)ARM_VSI3_BASE) |

| #define | ARM_VSI4 ((ARM_VSI_Type *)ARM_VSI4_BASE) |

| #define | ARM_VSI5 ((ARM_VSI_Type *)ARM_VSI5_BASE) |

| #define | ARM_VSI6 ((ARM_VSI_Type *)ARM_VSI6_BASE) |

| #define | ARM_VSI7 ((ARM_VSI_Type *)ARM_VSI7_BASE) |

Virtual Streaming Interface API for application firmware.

The VSI peripheral is accessed using the ARM_VSI_Type structure that defines registers for the following components:

8 VSI peripheral instances are mapped into the memory of a Cortex-M system:

The ARM_VSI_Type structure is defined in arm_vsi.h file as follows:

The ARM_VSI_Type::IRQ peripheral simulates an interrupt request. Set and Clear parameters have only write access and are used for triggering and clearing the interrupt. Status field indicates the interrupt state.

The ARM_VSI_Type::Timer peripheral is a simple counting timer with a 1MHz input frequency based on the time domain of the Arm Fast Model instruction set simulator. The Count value increments when the Interval value elapses.

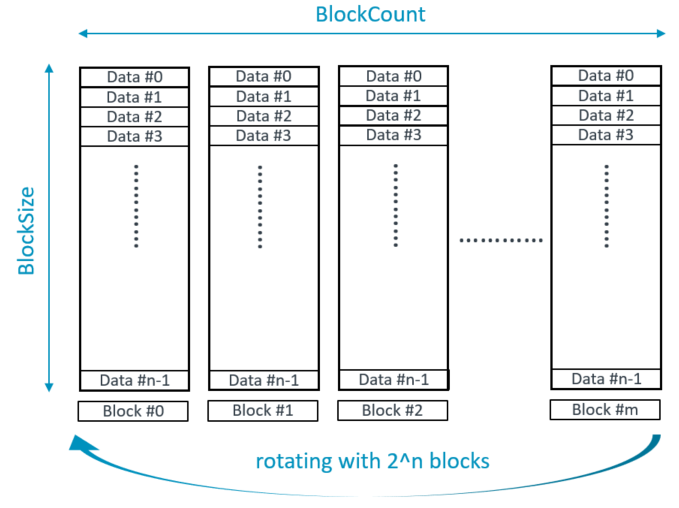

The ARM_VSI_Type::DMA controller accesses a rotating memory buffer as shown in the diagram below. Each block transfer increments the BlockIndex value (restarts when the buffer rotates).

| struct ARM_VSI_Type |

Structure type to access the virtual streaming interface.

The ARM_VSI_Type structure provides access to the VSI peripheral registers. The peripheral provides the following registers:

| Data Fields | ||

|---|---|---|

| struct ARM_VSI_Type.IRQ | IRQ |

Interrupt Request (IRQ) A group of registers that can enable and set/clear interrupt requests. |

| uint32_t | reserved1[60] | |

| struct ARM_VSI_Type.Timer | Timer |

Time counter with 1MHz input frequency. A simple counting timer with a 1MHz input frequency based on the time domain of the Arm Fast Model instruction set simulator. The Timer peripheral has the following registers:

|

| uint32_t | reserved2[61] | |

| struct ARM_VSI_Type.DMA | DMA |

Direct Memory Access (DMA) Controller. A virtual DMA controller which copies data from/to peripheral to/from memory. It has the following registers:

|

| uint32_t | reserved3[59] | |

| __IOM uint32_t | Regs[64] |

(R/W) User Registers Array of registers that allows to implement peripheral specific operations. |

| struct ARM_VSI_Type.IRQ |

| struct ARM_VSI_Type.Timer |

| struct ARM_VSI_Type.DMA |

Direct Memory Access (DMA) Controller.

| #define ARM_VSI0_BASE (0x4FF00000UL) |

VSI 0 Base Address

| #define ARM_VSI1_BASE (0x4FF10000UL) |

VSI 1 Base Address

| #define ARM_VSI2_BASE (0x4FF20000UL) |

VSI 2 Base Address

| #define ARM_VSI3_BASE (0x4FF30000UL) |

VSI 3 Base Address

| #define ARM_VSI4_BASE (0x4FF40000UL) |

VSI 4 Base Address

| #define ARM_VSI5_BASE (0x4FF50000UL) |

VSI 5 Base Address

| #define ARM_VSI6_BASE (0x4FF60000UL) |

VSI 6 Base Address

| #define ARM_VSI7_BASE (0x4FF70000UL) |

VSI 7 Base Address

| #define ARM_VSI0 ((ARM_VSI_Type *)ARM_VSI0_BASE) |

VSI 0 struct

| #define ARM_VSI1 ((ARM_VSI_Type *)ARM_VSI1_BASE) |

VSI 1 struct

| #define ARM_VSI2 ((ARM_VSI_Type *)ARM_VSI2_BASE) |

VSI 2 struct

| #define ARM_VSI3 ((ARM_VSI_Type *)ARM_VSI3_BASE) |

VSI 3 struct

| #define ARM_VSI4 ((ARM_VSI_Type *)ARM_VSI4_BASE) |

VSI 4 struct

| #define ARM_VSI5 ((ARM_VSI_Type *)ARM_VSI5_BASE) |

VSI 5 struct

| #define ARM_VSI6 ((ARM_VSI_Type *)ARM_VSI6_BASE) |

VSI 6 struct

| #define ARM_VSI7 ((ARM_VSI_Type *)ARM_VSI7_BASE) |

VSI 7 struct